Le décodage à seuil itératif de codes convolutionnels doublement orthogonaux (CSO2C) constitue un nouvel algorithme performant de correction d’erreurs. Cependant, les implémentations de ce type de décodeur qui ont été réalisées à ce jour ne sont pas suffisamment rapides pour les applications actuelles en télécommunication. De plus, ces implémentations ne supportent qu’un seul taux de codage R = 1/2.

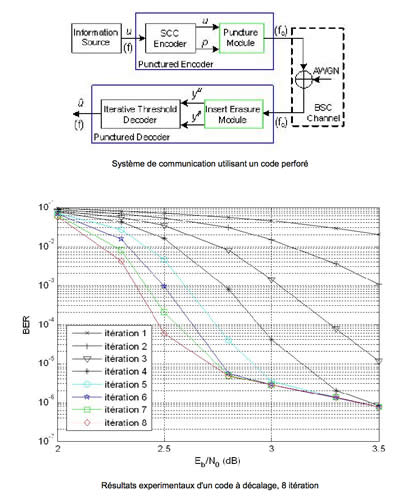

Dans le cadre de ce projet, un prototype à haut débit et de faible complexité du décodeur à seuil itératif a été réalisé. Une technique efficace de pipelinage a été développée et appliquée sur l’architecture du décodeur afin d’augmenter son débit qui a passé de 40 Mbps à 265 Mbps pour certains codes. D’autre part, sachant que la perforation de codes CSO2C permet d’augmenter le taux de codage, les modules de perforation correspondants ont été développés et intégrés dans le système. Ces modules supportent les codes à taux-compatible qui peuvent fonctionner à plusieurs taux de codage allant de R = 1/2 à R = 8/9.

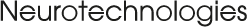

Finalement, une autre approche qui consiste à introduire les codes CSO2C à multi registre à décalage (MSR-CSO2C) a été utilisée pour augmenter le débit du décodeur. Les conditions de double orthogonalité des codes MSR-CSO2C ont été étudiées et un ensemble de codes MSR-CSO2C a été déterminé. Puis, un prototype du nouveau décodeur de codes MSR-CSO2C a été implémenté. Les résultats expérimentaux ont montré que les codes MSR-CSO2C offrent un compromis attrayant entre débit, complexité et performances d’erreurs. Ainsi, le prototype développé pourra être appliqué dans les systèmes de communication à haut débit.